CANFD中的SSP是什么?

- 2025-07-24 18:47:41

- 521

1.CAN通讯回读机制

在 CAN 通信中,控制器会通过采样收发器的 RX 引脚信号,来确认自己通过 TX 引脚发送的数据是否正确传输到总线。这种“回读”机制是实现仲裁判断和错误检测的关键。不过,由于 CAN 收发器在信号驱动和接收过程中存在固有的延迟,信号从 TX 输出、经过总线传播,再返回 RX 引脚,都会引入一定时间的滞后。

2. CAN采样点

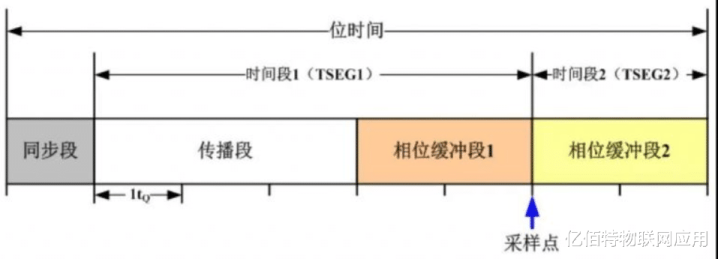

采样点即读取总线电平的时刻,并将读到的电平作为位值的点。位置在TSeg1结束处。比如采样点为80%,意思是(同步段+TSeg1)/(同步段+Tseg1+Tseg2) = 80%。

当一个比特时间(Bit Time)由固定数量的时间量子(Tq)组成,例如总计 10 个 Tq,其中同步段占 1 个 Tq,TSeg1 设置为 7,TSeg2 为 2,则采样点位于第 8 个 Tq,换算为百分比就是采样点出现在整个比特时间的 80% 位置,即:

Sample Point = (Sync_Seg + TSeg1) / Total_Tq = (1 + 7) / 10 = 80%

在进行位同步调整时,通过调节 TSeg1 和 TSeg2 的比例可以控制采样点的位置:如果 Prop_Seg + TSeg1 较小而 TSeg2 较大,采样点会向前移动;反之,Prop_Seg + TSeg1 较大而 TSeg2 较小,采样点则会向后靠近比特末尾。

此外,SJW(Synchronization Jump Width,同步跳转宽度)是定义在重同步过程中,采样点最多可以偏移的时间量(以 Tq 为单位)。SJW 决定了控制器在发生相位误差时,允许对采样点进行的最大修正范围。典型设置为 1~4 个 Tq。SJW 越大,系统对时钟误差的容忍度越高,抗干扰能力增强;但 SJW 设置过大可能会导致采样稳定性下降,影响通信精度或效率。

3. 什么是收发器延迟补偿

以 500kbps 的通信速率为例:每个bit的时间为 2000ns。若收发器有200ns 的信号延迟,相当于整个位周期的 10%,也就是说 RX 引脚上采样到的电平会比 TX 发出的信号滞后约 10% 的时间。如果我们按典型的采样点设置在 87% 来计算,那么由于延迟的存在,实际 RX 回读的采样时刻大约落在 77% 左右,依然处于显性或隐性位的稳定阶段,具有较好的采样裕度。

这正是 CAN 协议推荐将采样点设置在 75%~87% 的主要原因之一:为 TX 到 RX 的物理传输延迟预留足够的“时间窗”,确保即使存在一定延迟,控制器也能在有效电平区间内完成准确采样。

在 CAN FD 中,数据段支持更高的灵活比特率,例如 10Mbps,此时每个位的持续时间仅为 100ns。若收发器本身引入 200ns 的延迟,RX 引脚接收到的信号将滞后整整两个位周期,几乎无法与 TX 保持同步。这种级别的延时会严重干扰采样点的准确性,导致数据位被误判,即便调整采样点的位置也难以补救。为了应对这一问题,CAN FD 标准引入了一个关键机制:收发器延迟补偿(Transceiver Delay Compensation, TDC)。

4.什么是SSP (Secondary Sample Point)

在 CAN FD 协议中,为解决高速数据段中收发器延迟所引发的采样误差问题,标准引入了 二次采样点(SSP,Secondary Sample Point) 及 收发器延迟补偿机制(TDC,Transceiver Delay Compensation)。

当控制器处于仲裁阶段(通常波特率不超过 1Mbps)时,会利用 CAN 总线上的信号边沿(例如显性到隐性的跳变),通过比较本地 TX 引脚发出的信号与 RX 引脚回读的反馈信号之间的时间差,估算出收发路径的整体延迟(RX loop delay),该延迟主要由收发器内部驱动和接收电路引起。

在进入数据阶段(Data Phase)后,控制器会依据前述测得的延迟,对采样点进行动态后移调整,即在原定采样时刻基础上额外延迟一段时间,以确保 RX 引脚上的波形已经稳定到达,从而提升数据采样的可靠性和准确性。该实际采样位置即为 SSP。

通过这种延迟补偿机制,CAN FD 在支持高达数 Mbps 至 10 Mbps 的高速数据段通信时,依然能够保证同步精度和通信稳定性,有效避免因收发器延迟导致的位错误或 CRC 异常。